CEAT researcher opening doors in integrated circuit design

Wednesday, August 6, 2025

Media Contact: Erin Portman | Assistant Manager, CEAT Marketing and Communications | 405-744-2745 | erin.portman@okstate.edu

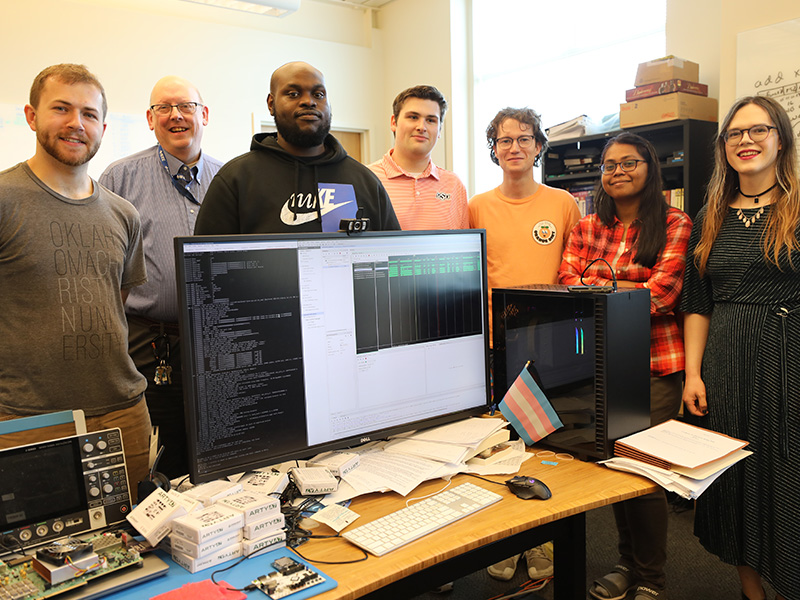

In the College of Engineering, Architecture and Technology at Oklahoma State University, Dr. James Stine is doing something quite radical: unlocking the black box of integrated circuit design for the next generation.

While giants of the semiconductor world guard their chip-building secrets behind billion-dollar walls, Stine, a professor of electrical and computer engineering and the Edward Joullian Endowed Chair in Engineering, is on a mission to make it open, teachable and — most importantly — accessible.

“Right now, if you want to teach IC design at a university, you have to work around expensive software licenses, restricted hardware models and a closed ecosystem,” he said. “We’re trying to change that.”

RAFT: Leveling the Playing Field in IC Design

That mission took a major leap forward with the launch of RAFT — Rapid Assured Fully Transparent IC Physical Design Capability.

Funded with $1.2 million from NASA, the project aims to create an open-source infrastructure for designing application-specific integrated circuits. The goal: to provide educators and students with the tools they need to build and test real chip designs without paying for commercial software.

For Stine, the project is part research, part revolution.

“With RAFT, we’re developing something that’s never existed at this scale: a transparent, fully documented, publicly available design environment that goes from concept to silicon,” he said. “It’s like building a second Silicon Valley — but in Stillwater, Oklahoma.”

RAFT doesn’t just support student learning. The tools and methodologies are also being used in collaborations with the U.S. Air Force and other government agencies that rely on specialized, secure chips for critical systems.

From Bitstreams to the Big Picture

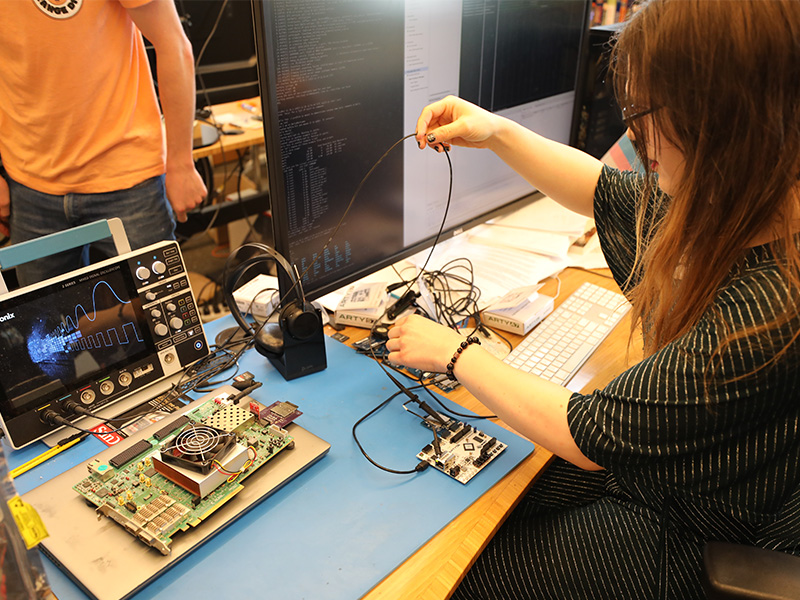

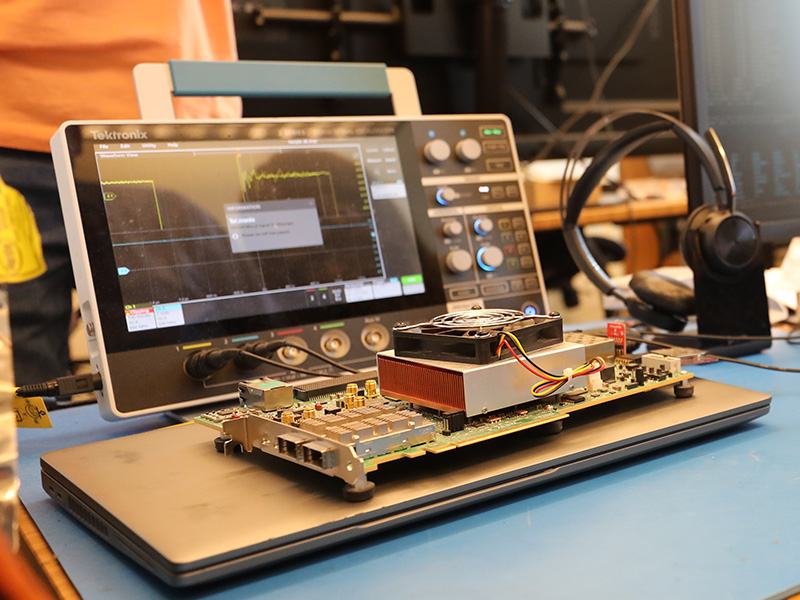

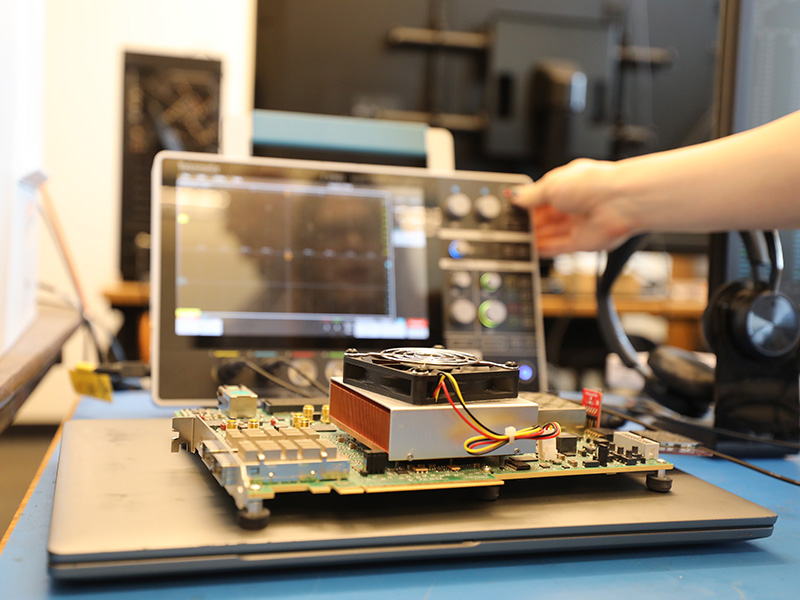

Stine’s research focuses on the intricate and often invisible elements that make modern electronics possible — arithmetic logic, signal processing and the physical layout of chips at the nanometer scale. Over the years, his lab has produced dozens of original chip designs, many of which have gone on to be used in real-world aerospace and defense systems.

But his work isn’t just about the hardware. It’s also about building a more comprehensive ecosystem for discovery.

“We’re training the next generation of engineers not just to use tools, but to build and improve them,” Stine said. “We want students to understand the math, the architecture and the physics — but also the power of open collaboration.”

That philosophy underpins much of his work. His lab has released several free and open-source tools, including CharLib, a platform for characterizing standard cell libraries as well as OpenRAM an open-source memory compiler. He has also made significant contributions to the development of open-source standard-cell libraries and System-on-Chip designs, enabling more accessible and customizable hardware platforms for education, research and industry.

These efforts have advanced the state of design automation, facilitated efficient integration of complex digital systems and promoted broader adoption of open semiconductor design methodologies. A notable example is Wally, a fully customizable RISC-V SoC open-source processor supporting both 32- and 64-bit architectures, developed to serve as a flexible platform for teaching, research and prototyping. Building on this work, the author is publishing a new textbook with Elsevier, scheduled for release in November, that details the design principles, implementation and educational applications of Wally and related open-source SoC development.

A Career of Design, A Vision for Impact

With more than 120 peer-reviewed publications and two decades of teaching under his belt, Stine has become a respected voice in Very Large Scale Integration education. In 2021, he was honored with the OSU Regents Distinguished Research Award, recognizing his pioneering efforts in ASIC design and undergraduate research mentoring.

He is also a longtime advocate for connecting academic research with national needs. His students often work on Department of Defense-funded projects, and he’s known for emphasizing real-world applications in every project his lab undertakes.

But talk to Stine for more than five minutes, and you realize his real passion isn’t just the science — it’s the students.

I see kids who come in thinking chip design is out of reach,” Stine said. “It’s too expensive, too complicated, too locked down. And then, one semester in the lab, they’re designing circuits and writing software that could power the next Mars rover. That’s what drives me.

Looking Ahead

With the RAFT platform entering pilot programs across multiple universities and collaborations expanding in aerospace and defense, Stine believes the momentum is just beginning.

“There’s a huge opportunity here. If we can give students the same tools used in industry — without the red tape — we can completely change who gets to innovate in this space.”

For Stine, the future of IC design isn’t just about making faster chips. It’s about opening doors — for students, for educators and for the technology that powers tomorrow’s world — while positioning OSU as a leader in semiconductor research, education and innovation.

Learn more about Dr. Stine's research